Toshiba, SanDisk Unveil 256 Gigabit 48-Layer 3D NAND ChipToshiba, SanDisk Unveil 256 Gigabit 48-Layer 3D NAND Chip

SanDisk's 3D NAND built using TLC (triple-level) die slated for mass production at Toshiba's new Fab 2 facility in Japan

August 5, 2015

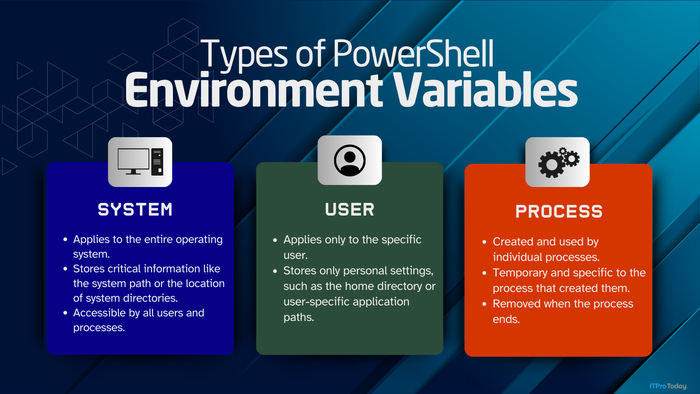

Toshiba and SanDisk announced their first 3-bit-per-cell (X3) 48-layer 3D NAND chip targeted for production.

The announcement rounds out most of the recent product news for 3D NAND technology, with Samsung's new 3D V-NAND, and Intel and Micron introducing 3D XPoint in a new non-volatile memory category. Korea's SK Hynix is expected to launch a 3D NAND product yet this year. SanDisk announced that it has reached an agreement with SK Hynix regarding trade secret litigation, modifying and extending their intellectual property licensing arrangement.

The new Toshiba and SanDisk chip is based on Bit Cost Scalable (BiCS) flash technology, a non-volatile, three-dimensional flash technology that Toshiba has been developing for some time. Having recently announced 48-layer NAND chips with 128Gbit (16GB) of capacity, the new chip now doubles that, with 256 Gigabit (32GB) of capacity.

SanDisk believes the new chip will be used in a wide variety of applications, ranging from consumer, client, mobile, and enterprise products. SanDisk selected this TLC (triple-level) die for its 3D NAND for mass production, which is slated to begin soon at Toshiba's new Fab 2 facility in Yokkaichi, Japan. Products are expected to ship in the first half of 2016.

About the Author

You May Also Like

.jpg?width=700&auto=webp&quality=80&disable=upscale)